JEDEC固态技术协会今天公布了DDR4内存标准中的部分关键属性,并宣布将在2012年年中正式发布新一代内存标准规范,相比于DDR3取得重大性能提升,同时继续降低功耗。

JEDEC固态技术协会宣称,DDR4将具备一系列创新特性,可带来更快的运行速度和广泛的实用性,包括服务器、笔记本、台式机、消费电子产品等等,其频率、电压和架构也都在进行重新定义,目标是简化新标准的迁移和部署。

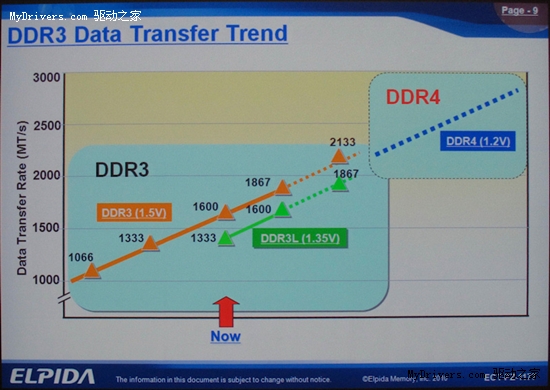

提议中的路线图显示,DDR4内存的VDDQ电压将设定在仅仅1.2V,并在未来进一步降低VDD电压,此外还会保证I/O电压的稳定。相比之下,DDR3标准版电压为1.5V,低压版也有1.35V。

DDR4内存每个针脚的数据传输率将达到1.6Gbps,最高会冲击3.2Gbps。考虑到DDR3就有望冲破1.6GT/s的极限,DDR4在未来应该还会具备更高的性能水准。其它提议中的性能改进还包括:DQ总线伪开漏接口(pesudo open drain interface)、2667MHz及更高数据率的低速档模式(geardown mode)、bank分组架构(bank group)、内部生成VreDQ电压、训练模式(training mode)改进。

DDR4架构上采用了8n预取的bank分组,包括使用两个或者四个可选择的bank分组,这将使得DDR4内存的每个bank分组都有独立的激活、读取、写入和刷新操作,从而改进内存的整体效率和带宽,尤其是在使用较小的内存粒度(memory granularity)的时候。

在此之前,三星和海力士已经分别造出了试验性的DDR4内存条。预计DDR4内存将于2014年投入商用,2015年即迅速普及。

DDR4其它正在开发中的特性:

- 三种数据带宽选择:x4、x8、x16

- 新的JEDEC POD12接口标准(1.2V)

- 时钟与闸门的差分信号

- 新的终端机制:DQ总线负责控制VDDQ终端,即使VDD电压衰减也能保持稳定。

- 常规和动态ODT:ODT协议的改进和新的停放模式(Park Mode)可以实现常规终端和动态写入终端,而无需惊动ODT针脚。

- 突发长度8,突发突变4。

- 数据屏蔽(data masking)

- DBI:帮助降低功耗、改进数据型号完整性,通知DRAM应该保存真正的还是倒置的数据。

- 新的数据总线CRC(错误校验):支持数据传输的错误校验功能,尤其有利于写入操作和非ECC内存应用。

- 新的指令/数据总线CA对等:一个新的低成本防范,用于指令和数据沿链接传输期间所有操作完整性的检验。

- 支持DLL关闭模式(DLL of mode)

(专业词汇翻译谬误之处敬请指正)