[趋势——新技术已然成熟]

DDR2是今年仅次于PCI Express的第二大技术革命,这次Intel联合了众多DRAM模组厂商的支持,让DDR2内存的价格在短短半年内数次跳水,到现在为止,DDR2的售价甚至比DDR SDRAM还低,现在的DDR2已经完全具备取代DDR SDRAM的实力。

DDR是在SDRAM的基础上发展而来,最大的特点就是采用了沿触发技术。为了满足双向触发的要求,DDR内存对芯片的结构进行了改进,使用了“2bit Prefetch(2bit预取)”技术。DDR的双向触发只发生在模组和内存控制器的接口部分,在DDR芯片内部,一个时钟周期依然只能传输一次数据。以4bit为宽的DDR芯片为例,Cell矩阵在时钟周期的上升沿触发生,一次传送8bit单位的数据,这8bit数据接着被转换成4bit单位的两道数据流进入I/O缓存中,然后在时钟频率周期的上升沿传送一道,下降沿传送一道。除了在性能上的增加之外,DDR内存模组的容量也得到了提高,但需要注意的是,DDR内存的延迟时间并不会因为双向触发技术而减半,和SDRAM依旧相同。

DDR266在133MHz下的物理传输频率可以达到266MHz,此时的信号干扰并不明显,但随着DDR333标准的出现,信号干扰问题开始突出,这也导致了初期良品率不高,DDR333芯片难以量产,这个问题在DDR400的时候变的更加严重。

DDR2时代到来:

DDR2内存起步为DDR2 400,发展出了533、667、*800。DDR2是在DDR的基础上改进而来,逻辑构架和物理结构都有了不少的进步,着重点放在了降低干扰,功耗和提高工作频率下的工作稳定性。

DDR使用“2bit Prefetch”技术,而DDR2内存拥有“4bit Prefetch”技术的数据预读取能力,也就是4位数据预取,这也是DDR2内存最重要的改进。虽然与DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但是在同等核心频率下,DDR2拥有两倍于DDR的数据传输率。

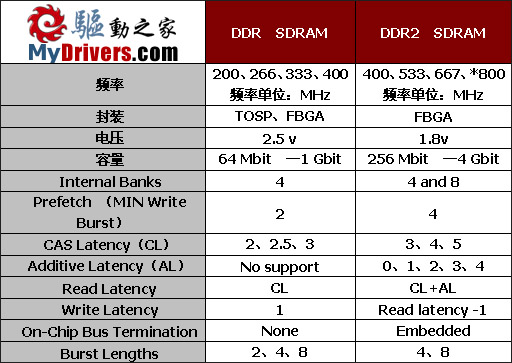

从上表可以看出,在同等核心频率下,DDR2的实际工作频率是DDR的两倍。这得益于DDR2内存拥有两倍于标准DDR内存的4bit预读取能力。换句话说,虽然DDR2和DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但DDR2拥有两倍于DDR的预读取系统命令数据的能力。也就是说,在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以达到400MHz。然而,这个方法虽然可以有效果提高内存带宽,但也有它最主要的缺点就是高延迟。内存延迟不取决于I/O缓冲区的工作频率或数据从存储单元进入总线的位宽多少。影响延迟的主要因素是内存存储单元自身的延迟。

从早期DDR2的表现来看,同DDR相比起来并没有占到多少便宜,反而是DDR2内存受高延迟的影响,性能要略逊色于同频的DDR内存平台。因此目前支持DDR2 SDRAM的内存厂商一些努力解决这个问题,现在他们取得了一定的成绩。在基于i915/925芯片组的平台上,早期DDR2-533 SDRAM内存仅能工作在4-4-4 timings的模式下。不过现在这种情况已经有所改观,许多内存制造商,特别象Corsair或OCZ等,都已经推出了支持3-3-3 timings规格、工作频率为533MHz甚至667MHz的DDR2 SDRAM内存模块。而这些内存模块并非通过超频获得的,而是完全符合JEDEC标准。

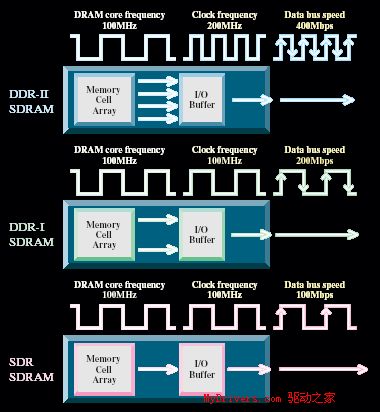

内存芯片的工作频率可细分成DRAM的核心频率,外部时钟频率和数据传输频率。对于SDRAM芯片来说,以上三者是等同的,也因此统称为工作频率。DDR的核心频率与外部时钟频率相同,但数据传输率是时钟的两倍。而DDR2则全然不同,三者完全分开。DDR2的核心频率只有时钟频率的一半,而时钟频率又是数据传输频率的一半,因为DDR2的数据传输频率是DRAM核心频率的四倍。正是因为这样的方式,使得人们误认为DDR2可以在每个时钟周期传输四次数据,但DDR2在每个时钟周期依然也只能传输两次数据,这与DDR是完全一样的。

现在的DRAM内部都采用4个bank的结构,每个bank由存储单元队列构成,存储单元队列通过行和列地址定位。从内存的读操作中可以了解到内存工作的几个瓶颈,它们分别是内存单元的再存储和预充电的延时,这个延迟属于bank内部的延迟,由于DRAM结构的限制这个延迟本身不太好解决。还有内部数据总线的频率限制,内部数据总线是连接DRAM颗粒中4个bank的总线,最后一个DRAM的瓶颈是输入/输出电路的延迟。

这样,在数据传输频率相同的情况下,DDR2芯片的核心频率只有DDR芯片的一半,而两者要供各的数据量必须相同,所以DDR2的Cell矩阵核心一次传输的数据量必须是DDR Cell矩阵核心的两倍才能将这个问题解决。现在我们知道了DDR2 Cell矩阵必须是芯片位宽的四倍,在配合上图,我们就可以知道DDR2芯片内部的工作原理和流程。对4bit的DDR2来说,Cell矩阵每个工作周期要提供16bit的数据,然后这些数据被分成两个数据流,每个数据流为8bit,再将这两个数据流分别传输给中转中转逻辑处理单位,这个步骤的时间是必须相同的。正如上图所显示的,后面的步骤就与DDR相同,8bit数据被转换为4bit数据然后分为两道数据流送入I/O缓存中,然后在钟频率周期的上升沿传送一道,下降沿传送一道。到此DDR2核心就能够以数据频率的1/4、时钟频率的一半运行。这就是“4bit Prefetch”技术。

DDR2内存采用FBGA封装,提供了比TSOP封装更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的提升提供了良好的保障。DDR2内存采用1.8V电压,相对于DDR标准的2.5V,降低了不少,从而提供了更小的功耗与更小的发热量。

片内终结器:

DDR2另外一个比较重要的改进就是采用了“片内终结器”,使得在DDR时代就一直困扰人们的内存兼容性问题得到了巨大的改善。DDR2直接在芯片内部设计了终结逻辑单元,而不是像有些DDR那样仅将电阻安装在模块上(正是由于每个数据线必须对应一个终结电阻,无形中增加了内存的成本和制造难度,且在终结电阻方面业界没有一个标准,致使DDR的内存兼容性问题极为严重)。由于终结逻辑单元自身所占用的晶体管数量极少,所以成本极低,且ODT的开关与否则完全由内存控制器控制,所以在内存兼容性方面,DDR2相比较于DDR内存来说更加出色稳定。